[ad_1]

Precision is paramount in the field of power electronics and circuit simulation. The veracity of simulation results hinges on the accuracy of the models employed for individual components. Be it IGBTs, silicon carbide or silicon MOSFETs, the reliability of simulation predictions rests on the precision of these models. The timeless phase “garbage in, garbage out” holds true.

The construction of system-level models is derived from datasheets, which are founded upon laboratory measurements of component characteristics like conduction, energy losses and thermal impedance. It constitutes most of the industry-standard models. However, these datasheet-based models are based on laboratory configurations and environments and don’t always reflect the wide range of conditions encountered in practical implementations. It is incorrect to assume that a model derived from a datasheet precisely depicts the complexities of a power electronics designer’s individual parasitic environment. The probability that a manufacturer’s experimental environment and a power electronics designer’s application environment will coincide is approaching zero. This conspicuous discrepancy gives rise to potentially significant inaccuracies in simulation outcomes, which frequently escalate to 20% to 30% or higher. For this to be mitigated, a paradigm transformation is necessary.

Onsemi’s Self-Service PLECS Model Generator (SSPMG) is a pioneering approach that empowers users to input their specific parasitic environment, crafting tailored PLECS models. Imagine purchasing a suit off the rack, never quite fitting perfectly. Much like a skilled tailor adjusting the garment for a flawless fit, the SSPMG customizes models precisely for individual applications.

The crux of this approach is simple: It’s not about onsemi’s lab results but about your application in your environment. By allowing users to fine-tune models to their unique environments, the accuracy of simulations sees a dramatic upswing. This emphasis on customization and precision isn’t merely a theoretical concept; it’s a real-world solution backed by tangible results. The industry is catching on, acknowledging the significant discrepancies arising from generic models and recognizing the power of tailoring simulations to individual needs.

The onsemi SSPMG simulation tool further allows users to customize high-density tables based on their electrical bias and temperature conditions. The goal is to ensure that the interpolation between data points within the table is accurate and to minimize the need for extrapolation, which often introduces errors in system simulation.

Onsemi has developed the SSPMG tool to include “corner models” representing the different fabrication conditions for the electronic product. Factors like threshold voltages, on-state resistance, breakdown voltages, capacitance and more exhibit variations based on the physics within the fab. Capturing these correlated parametric variations becomes critical, especially at a system level, as they significantly influence energy losses, conduction losses and temperature behavior of the devices under test.

Onsemi has made advancements by introducing PLECS models that are valid for hard- and soft-switching applications. Models are also valid for synchronous-rectification operation and only for the main switch operation. The tool can simulate various soft-switching applications, including DC/DC LLC and CLLC resonant, dual active bridge and phase-shifted full-bridge topologies.

Soft and hard switching

In power electronics, the distinction between soft switching and hard switching is crucial. For hard switching, the double-pulse test (DPT) is a reliable method for calculating losses. However, it becomes inaccurate for soft switching, which depends on topology and operation mode. Simulating soft switching with DPT is simply inaccurate.

To tackle this issue, the SSPMG precisely computes energy losses using a new transition-loss tester for a range of topologies, including phase-shifted full-bridge, DC/DC LLC and CLLC resonant. This specialized schematic enhances the precision of soft-switching models, a characteristic that is frequently disregarded in the industry. Engineers are now capable of acquiring accurate representations of their designs, thereby circumventing errors caused by incompatible simulation conditions. With our integrated capability, designers can rely on accurate models regardless of the switching topology, ensuring precision in simulations.

Switching-loss test

The DPT serves as a common method to gauge switching losses in semiconductor devices. It operates by cycling through specific steps: first, initiating the inductor current by activating the low-side switch, then measuring turn-off losses when the low-side switch is turned off at a certain current point. The inductor current continues, sustained by the high-side diode, assumed to remain constant due to its low voltage drop and brief duration. Finally, the low-side switch is turned on again, allowing the measurement of turn-on losses with a similar inductor current as during turn-off.

The setup, whether a half-bridge or quarter-bridge, impacts switching losses, notably due to the difference in characteristics between SiC Schottky diodes and MOSFET body diodes. The configuration, termed a “boost”-type tester, influences main switch losses as reverse-recovery current in the high-side switch/diode affects the lower-side switch losses at turn-on.

External factors, such as the inductor’s parasitic capacitor and PCB leakage inductance, significantly affect active switch losses. The inductor’s parasitic capacitor influences Eon and Eoff, impacting the overall losses. Additionally, PCB leakage inductance and components like ferrite beads to mitigate EMI alter the switching loop’s size and performance, affecting losses by slowing current ramping and allowing the voltage to reach lower levels.

The use of a DPT is an effective method to measure losses, especially when aiming for accuracy with minimal impact from parasitic elements. While onsemi’s advanced DPT serves well in comparing portfolio elements like die sizes and packages, it’s crucial to understand that losses in the tester environment won’t mirror those in a user’s application. Users’ specific parasitic elements greatly affect real-world losses, making it impractical to tailor a new setup for each design.

Modeling-based simulation is an alternative to this resource-intensive, limitation-laden and complex measurement-based method. By utilizing parametric simulations and highly accurate simulation models like onsemi’s physical and scalable SPICE models, power electronic designers can rapidly generate precise loss models. By facilitating the evaluation of multiple scenarios within a single run, these simulations provide insights that are both faster and more economical than laborious measurement techniques.

Onsemi’s SSPMG includes more than 30 parameters for fine-tuning the simulation schematics of DPT or transition-loss testers, which are utilized to extricate discrete and power module losses from SiC MOSFETs. By incorporating a wide range of application stages and scenarios and permitting the modification of gate-drive voltages, this all-encompassing tool enables power electronic designers to efficiently generate exceptionally precise PLECS loss models that are customized to their particular applications.

Case study: DC fast charger

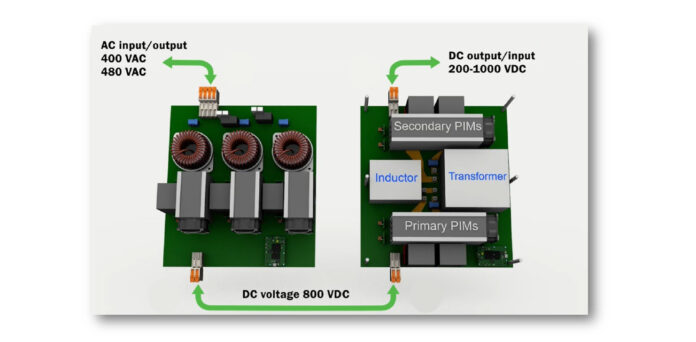

With one-of-a-kind capabilities, the Elite Power Simulator and SSPMG have had a substantial effect on product development cycles, particularly in sectors like DC fast charging, where optimizing design timelines is crucial. The tool deployment in a 25-kW DC fast charger—an essential component of the charging infrastructure for electric vehicles—is a prime example. In this instance, the simulator effectively facilitated a case study that compared SiC half-bridge modules of the first and third generations, accurately forecasting disparities in efficiencies that closely mirrored experimental findings.

Onsemi analyzed the comparison between measured data and simulation results in the 25-kW DC fast charger. The alignment between simulated and measured total module losses, albeit with minor deviations, showcases a promising correlation. However, the introduction of SSPMG-derived models into the Elite Power Simulator adds another layer to the analysis, incorporating layout parasitics and intricate details like motor winding capacitors and leading to accurate simulations.

An assortment of filters, amplifiers and gate drivers intertwined with SiC MOSFETs comprise the charger’s internal architecture. The intricate tango between the AC/DC active converter and the DC/DC converter is revealed through the utilization of various modules and topologies to achieve optimal performance. Evaluations show a curve of losses within ±10%, but simulations provide a more complex tale within ±5%.

The dynamic interplay between simulations and observed data shows the importance of employing precise modeling and exhaustive measurements when deciphering the performance of power electronics.

What’s new

The Elite Power Simulator and SSPMG are adaptable to diverse semiconductor technologies. While initially focusing on SiC products, both tools have recently expanded to the Field-Stop 7 IGBT products. This versatility ensures that engineers can leverage the tools across various devices, tailoring simulations to their specific requirements.

Reference:

[ad_2]

Source link